The previously developed tool that does the conversion has become very fragile to changes and its’ programming language differs from the rest of the flow. This IP-XACT file is interpreted and VHDL is generated based on its’ data. In this thesis project there is an existing register generator tool flow that uses IP-XACT as intermediate file format.

Register bank generation tools enable developers to quickly generate registers for a SoC module according to a register configuration file. Register banks are fast memory of SoC modules and each SoC module requires their own set of registers to suit module’s needs. Automation tools do repetitive tasks and one of these tasks would be generation of register banks. Tools are used for design, automation and verification purposes.

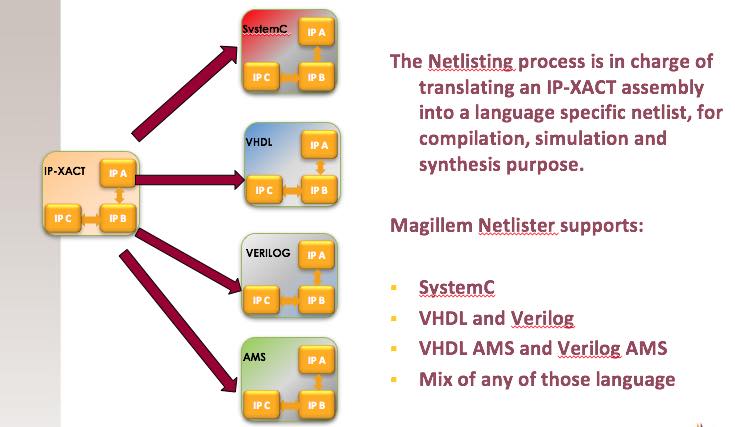

The information in the XML documents adhering to these XML schemas is called metadata. The XML schemas also allow you to describe designs in terms of IP block instances and interconnect between these instances. First it provides XML schemas that allow you to describe IP blocks you can think of this as an electronic datasheet of an IP block. You can get a free copy of the standard using the link on. IP-XACT is an IEEE standard to enable IP reuse and to enable tool flows to easily work with IP.

0 kommentar(er)

0 kommentar(er)